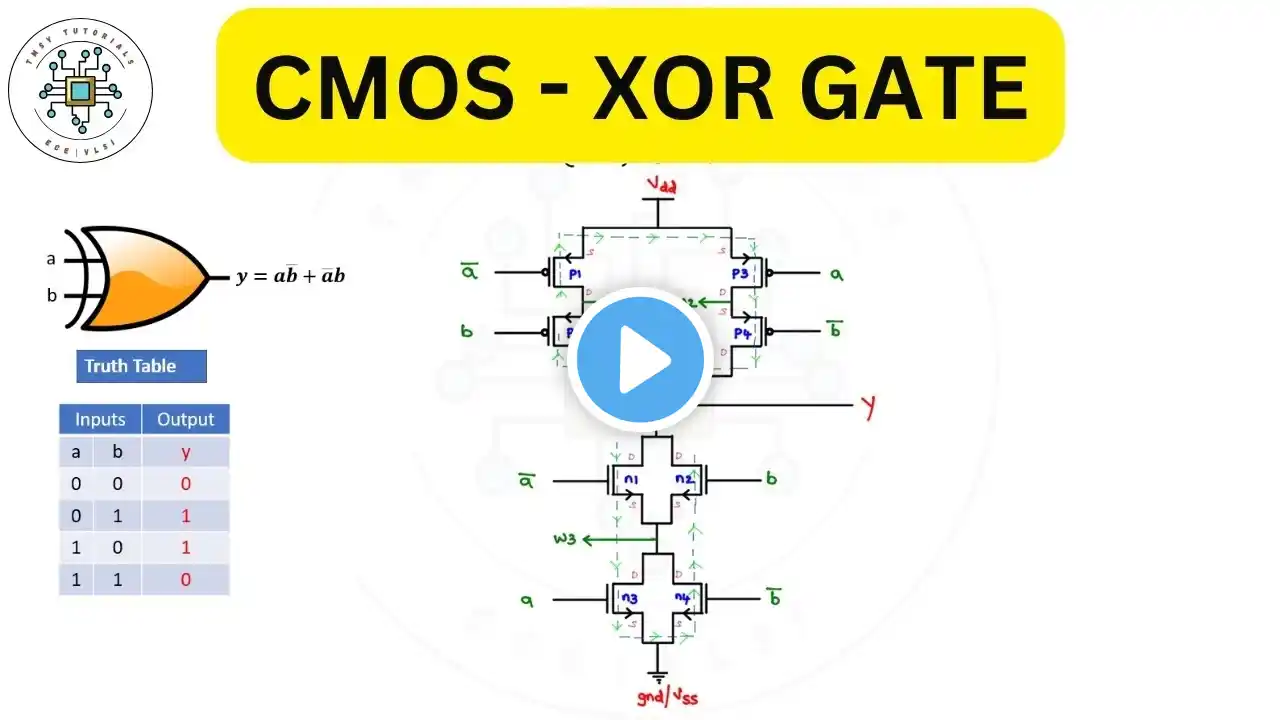

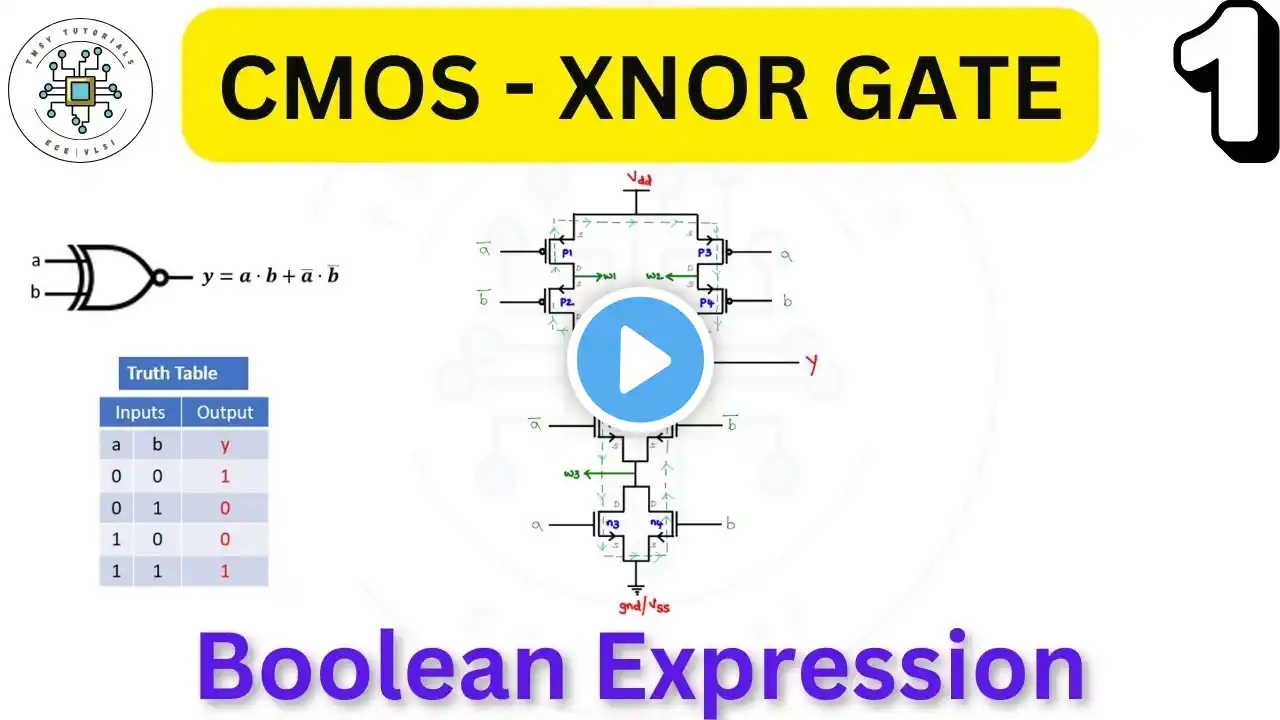

CMOS XNOR Boolean Expression to Schematic | Step-by-Step CMOS Design in VLSI | Part-1

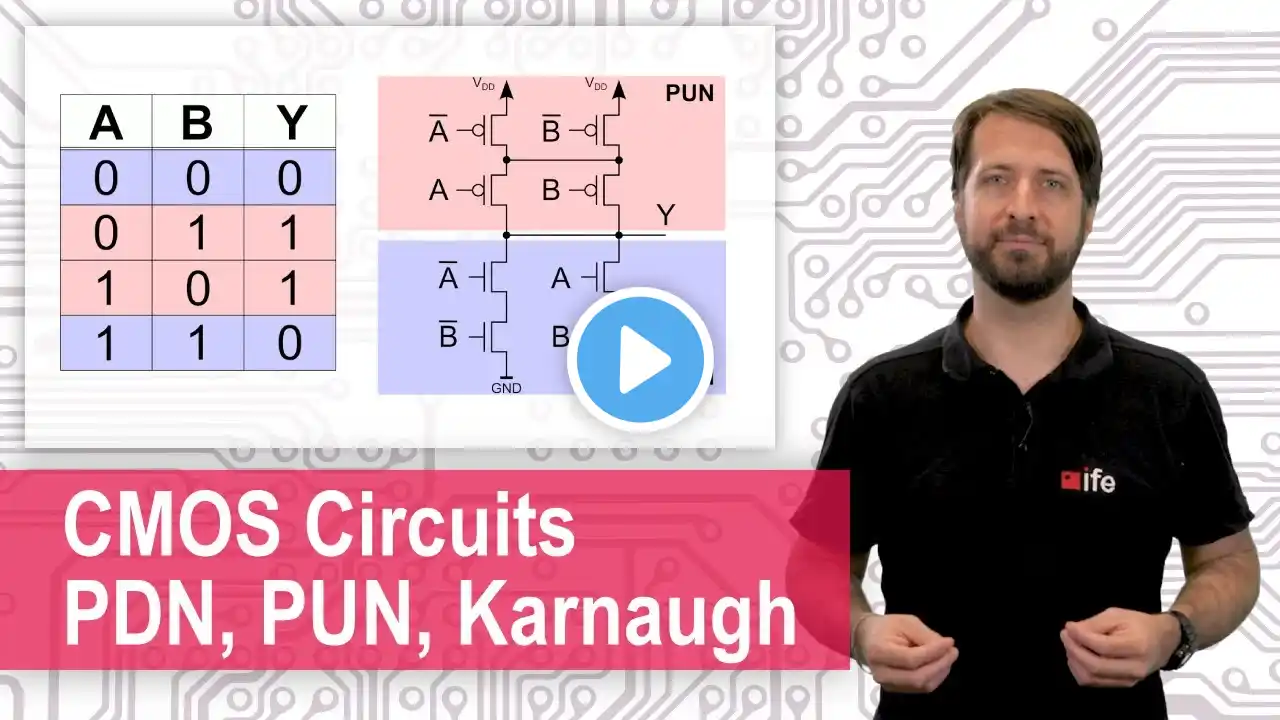

🧠 Description: Welcome to TMSY Tutorials, your trusted source for VLSI Design, CMOS Circuits, and Digital Logic Implementation tutorials! In this video, we explore how to derive and implement the CMOS XNOR gate schematic starting from its Boolean expression — an essential concept for VLSI students, digital designers, and standard cell engineers. This is Part-1 of our detailed CMOS XNOR series, where we focus on the logic derivation, Boolean simplification, and transistor-level schematic approach used in real-world ASIC and standard cell design flows. 🔍 Introduction The XNOR (Exclusive-NOR) gate, also known as the equivalence gate, outputs logic HIGH when both inputs are equal. Its Boolean function is Y = A·B + A’·B’. Understanding how to convert this Boolean expression into a CMOS transistor-level schematic is crucial for mastering custom digital design, standard cell creation, and EDA tool-based schematic design using Cadence Virtuoso or Synopsys Custom Compiler. The XNOR gate plays a major role in comparators, adders, error detection units, and clock domain crossing (CDC) circuits — making it an essential component in VLSI design and timing analysis. 🧩 Why CMOS XNOR Design Matters Foundation for Standard Cell Libraries: XNOR gates are key building blocks in arithmetic logic circuits. Used in Comparators and Adders: Essential for logic equality checks and bit-level operations. Crucial for Timing Analysis and STA: Understanding transistor connectivity helps in interpreting propagation delays. Relevance in ASIC Design Flow: From schematic capture to timing model generation using Cadence Liberate or Synopsys SiliconSmart. Important for CDC and Synchronization: Commonly used in parity checkers and phase detectors. 📘 Topics Covered Boolean expression of CMOS XNOR gate Logic simplification for transistor implementation Pull-up and pull-down network design Transistor-level schematic structure Simulation using EDA tools (Cadence/Synopsys) Power and delay considerations Application in synthesis and STA flows Real-world design use cases in digital systems 🎯 Call to Action Watch this Part-1 video till the end to learn how to convert the CMOS XNOR Boolean equation into a transistor-level schematic using systematic logic design steps. If you find this tutorial helpful, LIKE, SHARE, and SUBSCRIBE to TMSY Tutorials for upcoming Part-2, where we’ll discuss schematic simulation, waveform analysis, and timing verification using industry-standard EDA tools. 💬 Drop your questions or next topic requests in the comments — let’s keep growing the VLSI learning community together! 🔖 Hashtags #CMOS #XNORGate #CMOSSchematic #VLSIDesign #DigitalLogicDesign #CadenceVirtuoso #Synopsys #StandardCell #EDA #STA #TimingAnalysis #TMSYTutorials #VLSIMadeEasy #VLSITraining #SemiconductorDesign #CMOSLogic #CircuitDesign #CMOSXNOR #DigitalElectronics #VLSIProjects ✨ Hashtags for reach: #tmsytutorials #tmaharshisanandyadav #statictiminganalysis #sta #DTA #vlsi #vlsitraining #chipdesign #synthesis #physicaldesign #PrimeTime #tempus #redhawk #STAtools #DTAtools #STAinVLSI #DTAinVLSI #TimingAnalysis #timingclosure #VLSITutorials #VLSILearning #VLSIInterviewQuestions #VLSICourse #vlsijobs #asic #fpga #vlsidesign #rtldesign #RTLtoGDSII #digitaldesign #Voltus #cadence #synopsys #ansys #designcompiler #genus #Innovus #edatools #socdesign #chipverification #staticanalysis #dynamicanalysis #TimingVerification #STAflow #STAprocess #TimingReports #DelayCalculation #SetupTime #HoldTime #clocktreesynthesis #cts #signalintegrity #PowerAnalysis #IRDrop #EMAnalysis #NoiseAnalysis #GateLevelSimulation #PostLayoutSimulation #FunctionalVerification #RTLVerification #TimingSignoff #SignoffTools #STAengineer #DTAengineer #BackendDesign #frontenddesign #ChipImplementation #asicdesign #FPGAprototyping #icdesign #semiconductors #SiliconDesign #vlsiprojects #VLSIResearch #StandardCells #LibraryCharacterization #eda #hardwaredesign #logicdesign #circuitdesign #digitalelectronics #edasoftware #ChipTapeout #VLSILab #VLSItools #NetlistAnalysis #SDF #LibFiles #SDFAnnotation #TimingLib #TimingClosureFlow #designflow #RTL2GDS #EDAflow #SemiconductorEngineering #SoCtiming #AdvancedNodes #TimingOptimization #ClockDomainCrossing #VLSItips #ece #engineering #osmaniauniversity 📚 Watch More VLSI Tutorials: YouTube: / @maharshisanandyadav Udemy: https://www.udemy.com/course/digital-... Instagram: / vlsi.tmsy.tutorials LinkedIn: / t-maharshi-sanand-yadav